Фінансові новини

- |

- 14.05.26

- |

- 09:19

- |

-

RSS

RSS - |

- мапа сайту

Авторизация

TSMC випустила перший чіп за покращеним 3-нм техпроцесом N3E, але до масового виробництва ще далеко

13:25 26.10.2022 |

Розробник напівпровідникових мікросхем Alphawave повідомив, що випустив перший в індустрії дослідний зразок чіпа з використанням покращеного 3-нм технологічного процесу N3E від компанії TSMC. Наголошується, що тестовий зразок успішно пройшов усі необхідні тести.

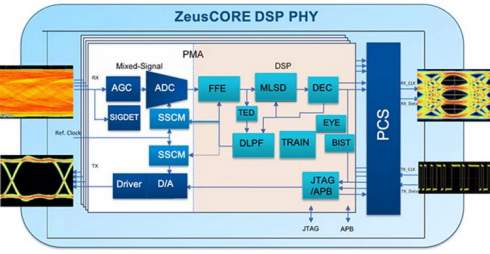

Для Alphawave випустили зразок чіпа ZeusCORE100 1-112Gbps NRZ/PAM4 Serialiser-Deserialiser (SerDes), що представляє собою пару функціональних блоків, які зазвичай використовуються у високошвидкісному зв'язку, для перетворення даних між послідовним і паралельним інтерфейсами в обох напрямках. Він підтримує різні нові стандарти інтерфейсів, включаючи 800G Ethernet, OIF 112G-CEI, PCIe 6.0 і CXL3.0. Подібні чіпи переважно застосовуються для коменікацій у серверних системах.

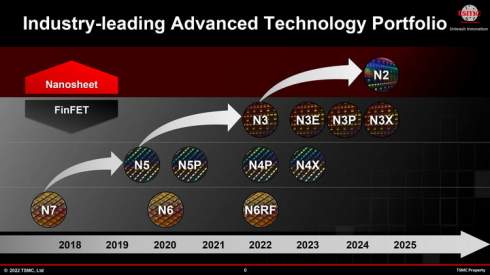

TSMC планує представити п'ять варіацій 3-нм техпроцесу протягом двох-трьох років. Звичайна версія техпроцесу N3 буде використовуватися провідними клієнтами контрактного виробника чипів, наприклад тієї ж Apple. З введенням другого покоління 3-нм техпроцесу (N3E) планується прискорити, а також збільшити обсяги випуску мікросхем, підвищити рівень їхньої продуктивності та енергоефективності.

Очікується, що чіпи на базі вдосконаленого 3-нм техпроцесу N3E отримають ширше використання в порівнянні з мікросхемами на базі стандартного техпроцесу N3, проте старт масового випуску чіпів на основі техпроцесу N3E очікується не раніше середини 2023 року, тобто через рік після початку масового виробництва чіпів згідно з нормами N3.

Після переходу до масового виробництва чіпів за нормами N3E компанія TSMC планує перейти до випуску мікросхем на техпроцесах N3P і N3S, які будуть варіантами оптимізації N3E під різні класи застосувань. N3P орієнтується на високопродуктивні чіпи, а N3S - на енергоефективні чіпи з підвищеною щільністю транзисторів. Обидва техпроцеси заплановані на 2024 рік. До 2025 року, коли компанія почне освоювати наступний рівень напівпровідникових норм, з'явиться ще один техпроцес 3-нм класу - N3X. На його базі будуть випускатися високопродуктивні процесори, для яких важливим є використання високих робочих струмів та тривала робота на підвищених тактових частотах.

ТЕГИ

ТОП-НОВИНИ

ПІДПИСКА НА НОВИНИ

Для підписки на розсилку новин введіть Вашу поштову адресу :

Міністр оборони США Піт Гегсет заявив, що Пентагон направив своїх

військових до України, щоб навчитися застосовувати дрони на полі бою.

Міністр оборони США Піт Гегсет заявив, що Пентагон направив своїх

військових до України, щоб навчитися застосовувати дрони на полі бою. Кабінет міністрів України видав постанову, якою розширив перелік країн, громадяни яких можуть набувати громадянство України у спрощеному порядку.

Кабінет міністрів України видав постанову, якою розширив перелік країн, громадяни яких можуть набувати громадянство України у спрощеному порядку. Міністри оборони України і Німеччини Михайло

Федоров та Борис Пісторіус підписали в Києві лист про наміри щодо

запуску Brave Germany - спільної програми для розвитку оборонних

технологій та підтримки інноваційних стартапів.

Міністри оборони України і Німеччини Михайло

Федоров та Борис Пісторіус підписали в Києві лист про наміри щодо

запуску Brave Germany - спільної програми для розвитку оборонних

технологій та підтримки інноваційних стартапів.

Велика Британія готується розпочати переговори щодо приєднання до

плану Європейського Союзу з надання Україні кредиту на суму 90 млрд

євро.

Велика Британія готується розпочати переговори щодо приєднання до

плану Європейського Союзу з надання Україні кредиту на суму 90 млрд

євро. Франція запропонувала Греції угоду про передачу всіх її винищувачів

Mirage 2000 Україні в обмін на вигідні умови придбання винищувачів

Rafale у компанії Dassault Aviation.

Франція запропонувала Греції угоду про передачу всіх її винищувачів

Mirage 2000 Україні в обмін на вигідні умови придбання винищувачів

Rafale у компанії Dassault Aviation. Дізнайтеся, як облаштування тренажерного залу в офісі підвищує продуктивність команди. Поради щодо вибору професійного фітнес-обладнання від бренду Besport.

Дізнайтеся, як облаштування тренажерного залу в офісі підвищує продуктивність команди. Поради щодо вибору професійного фітнес-обладнання від бренду Besport. АЗОВ.ONE та Obmify оголосили спільний збір: чим допомогти, як підтримати, куди підуть гроші. Донатьте і беріть участь у розіграші за посиланням в статті

АЗОВ.ONE та Obmify оголосили спільний збір: чим допомогти, як підтримати, куди підуть гроші. Донатьте і беріть участь у розіграші за посиланням в статті Американська компанія Tesla повністю припинила

виробництво своїх флагманських електромобілів Model S та Model X, які

протягом 14 років були символом переходу світу до електромобільності.

Американська компанія Tesla повністю припинила

виробництво своїх флагманських електромобілів Model S та Model X, які

протягом 14 років були символом переходу світу до електромобільності.

Представники компаній, таких як Volkswagen, BMW і Mercedes-Benz та

постачальники галузі, зустрічаються з посадовими особами Європейського

Союзу, щоб домогтися подальшого пом'якшення запропонованих правил щодо

викидів CO2.

Представники компаній, таких як Volkswagen, BMW і Mercedes-Benz та

постачальники галузі, зустрічаються з посадовими особами Європейського

Союзу, щоб домогтися подальшого пом'якшення запропонованих правил щодо

викидів CO2. Google оголосила про нову функцію Pause Point у складі Android 17. Вона додає обов'язкову 10-секундну паузу перед запуском будь-якого застосунку, який користувач позначив як відволікаючий.

Google оголосила про нову функцію Pause Point у складі Android 17. Вона додає обов'язкову 10-секундну паузу перед запуском будь-якого застосунку, який користувач позначив як відволікаючий. Колектив Meta протестує проти використання програми, яку компанія

встановила на робочі ПК для відстеження рухів їхніх комп'ютерних миш.

Колектив Meta протестує проти використання програми, яку компанія

встановила на робочі ПК для відстеження рухів їхніх комп'ютерних миш.  Google і SpaceX ведуть переговори про запуск орбітальних дата-центрів у

космосі, повідомляє The Wall Street Journal із посиланням на джерела,

знайомі з ситуацією.

Google і SpaceX ведуть переговори про запуск орбітальних дата-центрів у

космосі, повідомляє The Wall Street Journal із посиланням на джерела,

знайомі з ситуацією. Sony розпочала розробку своїх носимих охолоджувальних пристроїв Reon

ще у 2017 році, а тепер представила найпросунутішу й найефективнішу

модель - Reon Pocket Pro Plus. Вперше вона стане доступною не лише в

Японії, а й у Великій Британії та Європі

Sony розпочала розробку своїх носимих охолоджувальних пристроїв Reon

ще у 2017 році, а тепер представила найпросунутішу й найефективнішу

модель - Reon Pocket Pro Plus. Вперше вона стане доступною не лише в

Японії, а й у Великій Британії та Європі Компанія Google оголосила

про запуск нової системи на базі ШІ Gemini Intelligence, яка

інтегрується в Android‑пристрої. За словами компанії, вона буде

допомагати користувачам виконувати повсякденні завдання, зберігаючи

контроль над даними та конфіденційність.

Компанія Google оголосила

про запуск нової системи на базі ШІ Gemini Intelligence, яка

інтегрується в Android‑пристрої. За словами компанії, вона буде

допомагати користувачам виконувати повсякденні завдання, зберігаючи

контроль над даними та конфіденційність.

Ринок електромобілів в Україні поступово відновлюється після провалу,

зафіксованого на початку року, пов'язаного зі скасуванням податкових

пільг на них.

Ринок електромобілів в Україні поступово відновлюється після провалу,

зафіксованого на початку року, пов'язаного зі скасуванням податкових

пільг на них.  Україна впроваджує ШІ-рішення у війну разом з американською компанією

Palantir Technologies. Про це повідомив міністр оборони України Михайло

Федоров після зустрічі із CEO Palantir Technologies Алексом Карпом.

Україна впроваджує ШІ-рішення у війну разом з американською компанією

Palantir Technologies. Про це повідомив міністр оборони України Михайло

Федоров після зустрічі із CEO Palantir Technologies Алексом Карпом.

Фахівці підрозділу Threat Intelligence Group компанії Google заявили, що

зафіксували спробу кібератаки, в якій злочинці використали штучний

інтелект для створення експлойту нульового дня проти популярного

веб-інструменту адміністрування систем.

Фахівці підрозділу Threat Intelligence Group компанії Google заявили, що

зафіксували спробу кібератаки, в якій злочинці використали штучний

інтелект для створення експлойту нульового дня проти популярного

веб-інструменту адміністрування систем.  Поки більшість світу все ще намагається зрозуміти, чим 5G кращий за

старий добрий LTE, у Китаї вирішили не чекати, поки маркетинговий пил

вляжеться.

Поки більшість світу все ще намагається зрозуміти, чим 5G кращий за

старий добрий LTE, у Китаї вирішили не чекати, поки маркетинговий пил

вляжеться. Апетит сучасних систем штучного інтелекту до електроенергії вже давно

перестав бути проблемою лише екологів та перетворився на головний біль

для інженерів.

Апетит сучасних систем штучного інтелекту до електроенергії вже давно

перестав бути проблемою лише екологів та перетворився на головний біль

для інженерів.  Поки індустрія розважає публіку обіцянками про повне самоврядування,

бюрократи з Вашингтона вирішили, що пора перевірити, як системи допомоги

водію працюють насправді.

Поки індустрія розважає публіку обіцянками про повне самоврядування,

бюрократи з Вашингтона вирішили, що пора перевірити, як системи допомоги

водію працюють насправді.  NVIDIA оголосила

про інвестицію на $300 мільйонів у Corning для багаторічного

комерційного та технологічного партнерства з метою розширення

виробництва передових рішень оптичного зв'язку для живлення

інфраструктури штучного інтелекту.

NVIDIA оголосила

про інвестицію на $300 мільйонів у Corning для багаторічного

комерційного та технологічного партнерства з метою розширення

виробництва передових рішень оптичного зв'язку для живлення

інфраструктури штучного інтелекту.